Current Design V:2.0.0

Design Details

-

Chip Specs

Chip: Radiation-Tolerant PolarFire® SoC FPGA (RTPFS460ZT)Radition: 100 Krad Total Ionizing DoseSafety: Built in monitor core with 4 application cores -

Port Specs

Ethernet: 2x Gigabit Ethernet MACFPGA I/O: 516 configurable pinsUART: 5 UART ports built in -

Design Specs

Usage: TBD on real flight hardwarePower: TBD on real flight hardwareTiming: TBD on real flight hardware

To be done next

- Potentially accelerating encryption and decryption on fabric using open source crypto IP cores

- Design and develop DMA steams from memory to transiever to potentially reduce CPU load when downlinking data from nonvol memory

- Run more system level tests once more hardware starts to come in to get baseline data.

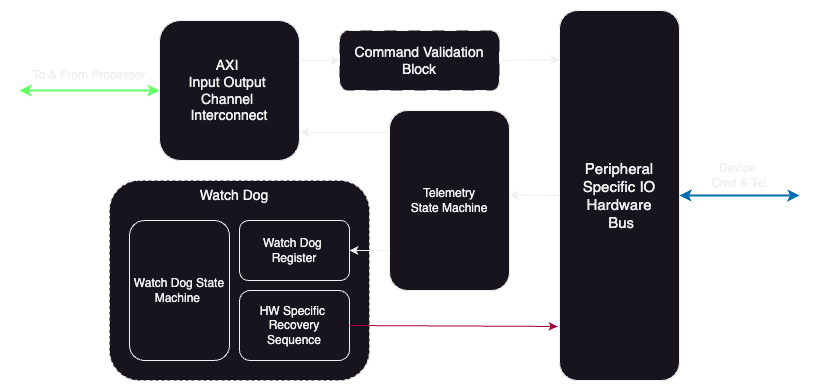

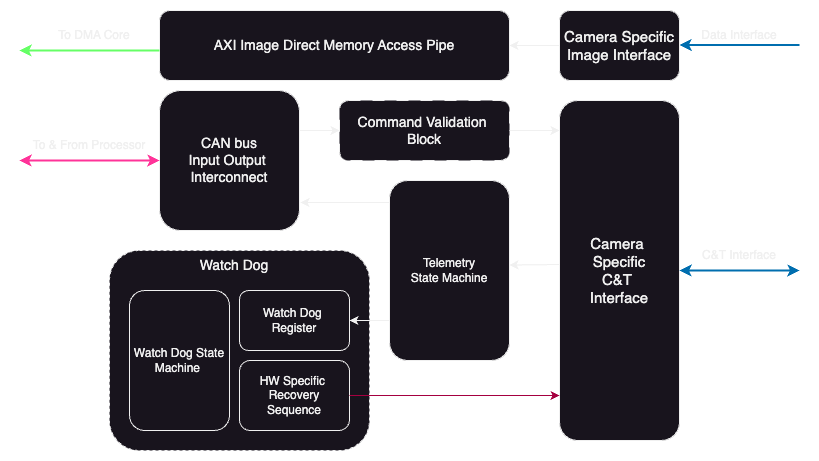

Logic Blocks

Logic block in fabric to manage COTs perhiperals

Logic block in fabric to manage the cameras

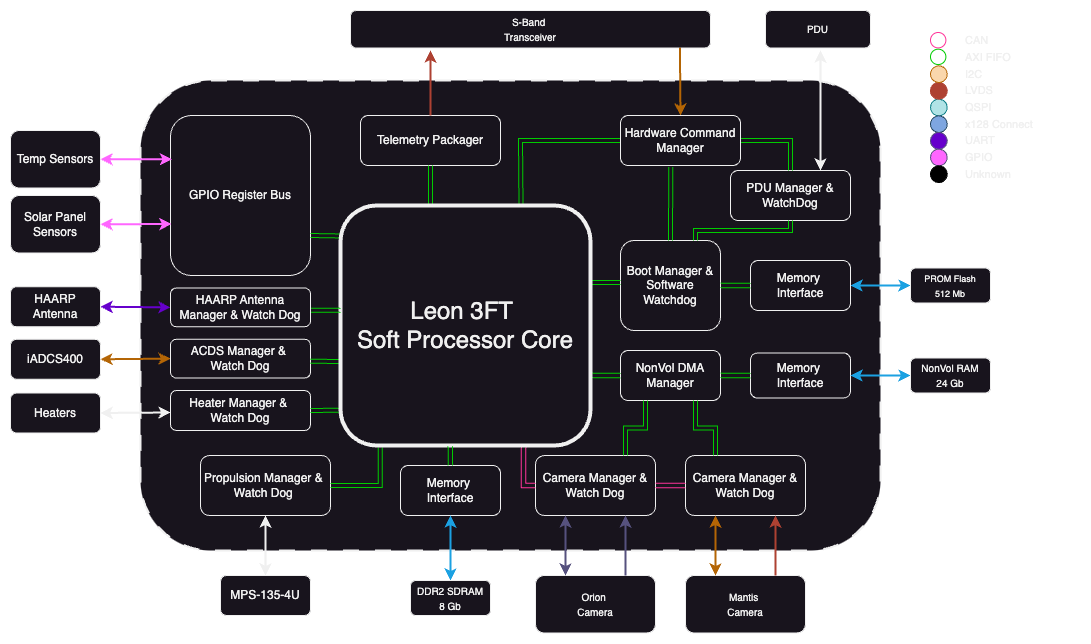

Previous Design V:1.2.1

Reasons for sunsetting version 1

MicroChip RTG-4 with Leon3FT Core

-

Techincal

Design Complexity: Since the RTG-4 is purely fabric everything must be designed and validated (including the softcore). This increase the complexity of the FPGA board design and will end up costing more time and money.Processor: For the RTG-4 the Leon3 softcore was the processor selected to run the software. On paper, this core is quite solid since it utilizes the Sparc v8 architecture and has built in fault tolerance but in practice, this core is old and dated. Furthermore, the softcore is rather slow compared to a hardcore. -

Support

Cost: Gaisler is a great company but they are extremely expensive. To use and test with their fault tolerant cores, one needs a paid subscription.Documentation & Usability: Grlib documentation and Ip core setup is extremely great once the learning curve is passed. That being said, given that this project will be multigeneration between several classes of students, having documentation that is easier to parse is critical and simpler tools are preferred.Community: Tragically, given the age of the technology, there isnt much of an active community around the softcores themselves making them extremely difficult and time consuming to debug and program. -

Other Considerations

Heratige: The RTG-4 with the Leon3FT cores have a ton of hertiage in space. Especially in the orbits that we expect TERP-RAPTOR to be in. This maks this design more desirable.

Radiation-Tolerant PolarFire® SoC

-

Techincal

Design Complexity: Unlike the RTG-4, the design complexity on this chip is signfianctly reduced since the 5 RISC-V cores and their supporting circuitry are hardwired into the chip. This reduces development times and simplifies tool chains in the software.Processor: Since the 5 cores are hardwired, they tend to run signfincatly faster than the Leon3FT soft cores. Furthermore, since the cores are not soft, they are more resilient to radiation since their configuration would not be floating. Finally, this chip comes with a built in monitor core reducing the design overhead for the dev (me). -

Support

Cost: Microchip also has transaction based services, but both boards would have required them so that does not change much. Other than that, there are no other licenses required.Documentation & Usability: Due to RISC-V's opensource nature, there are tons of resources on the internet that can help bring people up to speed on the archicture. Also since its newer, students are tend to be far more acustom to RISC-V vs SPARC.Community: The RISC-V community is massive. This is good because it means that debugging issues in RISC-V cores will be easier and there will be more resources on the internet for RISC-V. -

Other Considerations

Heratige: This chip is rather new and does not much heratige in the orbits that we want to be in.End of Life: RISC-V is becoming a bigger deal in space and that everyone is already migrating to RISC-V, there will be far more interest for groups to fly their RISC-V software to raise TRL levels.